近日,人机物融合智能计算团队的研究成果“Hierarchical Partitioning-Based Inter-Chip Redistribution Layer Routing for Fan-Out Wafer-Level Packaging”被集成电路设计自动化领域顶级期刊IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD, CCF-A类) 全文接收。该成果第一作者为西北工业大学计算机学院本科生徐浩洋(指导老师黄兴教授),这是学院实施本科生“拔尖筑基荣誉导师计划”以来的又一突出成效。此外,该研究由西北工业大学牵头,同中国香港、美国等高校和企业合作完成,彰显了计算机学院大力推进国际化办学的宗旨。

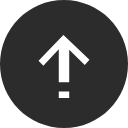

图1 所示设计方法的总体流程

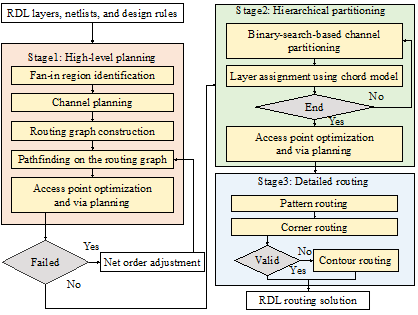

近年来,随着我国科技界对芯片领域“卡脖子”关键技术的攻坚,集成芯片和芯粒技术受到了前所未有的高度重视,而扇出型晶圆级封装(FOWLP)工艺因其高集成度、低功耗、高性能等优势,在高性能计算、人工智能等领域得到了广泛应用。该研究聚焦集成电路先进封装设计领域,针对FOWLP工艺下芯粒互连设计所面临的高密度布线冲突、通孔布局优化困难、寄生效应影响信号完整性等突出问题,提出了一种基于层级划分的重分配层布线设计流程,通过采用全局通道规划、接入点优化、线网层分配优化等策略,有效提高了布线效率,实现了高布通性、短线长、低干扰等目标,为解决高密度芯粒互连设计中的关键问题提供了新思路。

图2 芯粒互连设计结果

该论文一作徐浩洋同学目前本科就读于西北工业大学计算机学院,拥有扎实的计算机科学基础和丰富的竞赛经历,曾在国际大学生程序设计竞赛(ICPC)亚洲区域赛中斩获两枚金牌,并在2023和2024年ICPC世界总决赛中跻身决赛圈,取得了西工大在ICPC赛事上的历史最佳名次。IEEE TCAD是中国计算机学会在体系结构领域推荐的A类期刊,重点关注包括模拟电路、数字电路等在内的集成电路计算机辅助设计最新研究进展。西北工业大学计算机学院将继续为学生提供丰富的科研资源和前沿技术平台,助力更多优秀学子在国际舞台上展现创新能力和科研实力。

(审稿:郭斌)